Poznámka: Tento článek obsahuje výňatky z obsahu Virtual VOICE 2021 Best Paper, o kterém hlasovali účastníci konference. Jonvyn Wongso, Daniel Marstein a Krishna Vangapalli z Microchip Technology byli spoluautory původního článku a jejich výzkumné a vývojové úsilí bylo pro tento projekt neocenitelné.

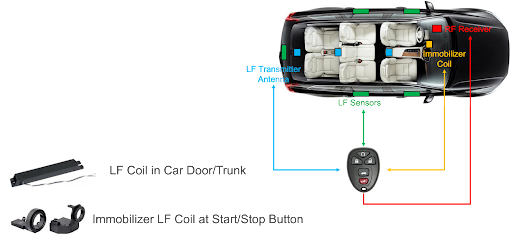

Technologie Passive Entry Passive Start (PEPS) se na automobilovém trhu stala standardem pro bezklíčové ovládání. Bezpečný bezdrátový komunikační systém PEPS umožňuje zamknout a odemknout vozidlo, nastartovat a zastavit vozidlo bez fyzického použití klíče. Elektronické funkce zabudované do klíčenky pro interakci s vozidlem (viz obrázek 1) zahrnují pasivní start a stop, pasivní zámek, dálkový bezklíčový vstup, imobilizér, probuzení klíčenkou a lokalizaci klíčenky. Tyto funkce jsou řízeny primárními moduly zabudovanými v samotném FOB. Imobilizér umožňuje nastartovat vozidlo, když je baterie v ovladači vybitá, přiložením ovladače ke startovacímu tlačítku a jeho stisknutím.

Obrázek 1: Tento diagram ilustruje, jak komponenty v přívěsku na klíče odpovídají funkčnosti v samotném voze.

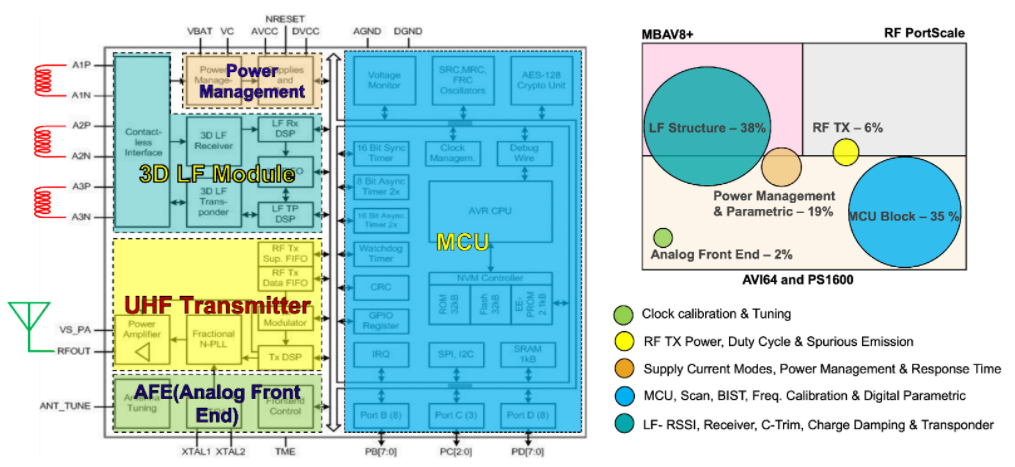

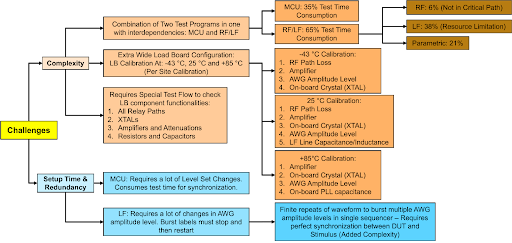

Ekosystém PEPS-to-vozidlo vyžaduje ke svému fungování několik klíčových modulů, které zahrnují nízkofrekvenční (LF) vysílač, imobilizér, radiofrekvenční (RF) vysílač (klíčenka) a transceiver (na straně vozidla), stejně jako mikrokontrolér. (MCU). Každý modul v přívěsku na klíče představuje specifické testovací výzvy a omezení, což vyžaduje testovací plán a tok optimalizovaný pro testování obvodu ovladače, jak je znázorněno na obrázku 2.

Obrázek 2: Architektura přívěsku na klíče zobrazuje hlavní komponenty v rámci přívěsku na klíče a znázornění toho, jak jsou jednotlivé komponenty testovány na testovacím systému Advantest V93000.

Procenta pokrytí vpravo nahoře na obrázku 2 představují celkovou dobu testování toku testu. Přibližně dvě třetiny testovacího pokrytí jsou věnovány struktuře LF (analogové) a MCU (digitální), dalších 19 procent se zaměřuje na řízení spotřeby a parametrické testy. Zbývajících 6 procent testovacího pokrytí zahrnuje testování RF modulu s přenosovou funkcí v pásmu pod 1 GHz bez schopnosti RF příjmu.

Kombinace testovacích požadavků pro přizpůsobení se všem různým technologiím umístěným v klíčence PEPS z něj dělá ideální zařízení pro demonstraci všestrannosti testovací platformy Advantest V93000 SoC, včetně kolíkových karet AVI64 a PS1600. Testovací řešení je navrženo s komplexními metodikami pro testování každého modulu v klíčence. Bilance tohoto článku shrnuje klíčové aspekty testovacího přístupu.

Prvky metodiky testování PEPS

Digitální testování využívá dvě standardní metody pro komunikaci s IC:

- Sériové programovací rozhraní (SPI) – Standardní komunikační protokol se používá k testování všech ne-MCU (nedigitálních) struktur prostřednictvím přímého přístupu do RAM. Vzhledem k pomalé komunikační rychlosti ve srovnání s protokolem HVSP je však doba programování do EEPROM přibližně 10 ms na bajt.

- Vysokonapěťové sériové programování (HVSP) – Používá se pro test jádra FLASH a MCU s rychlým přístupem k EEPROM, tento proprietární protokol je mnohem rychlejší než SPI, s dobou programování FLASH a EEPROM 3 až 4 ms na stránku (každá stránka je 16 dlouhé bajty).

Jedním z klíčových digitálních testů, které je třeba provést, je změřit čas na naprogramování stránky na FLASH (16 bajtů). Doba dokončení programu stránky se mezi zařízeními liší. Typickou testovací metodou měření a detekce konce programovacího času je implementace operačního kódu čítače shodné smyčky do vzorového vektoru, když zařízení po dokončení programovací události potvrdí stav kolíku na vysokou úroveň. Implementace této metody však zakazuje použití funkce Time Measurement Unit (TMU) PS1600 na stejném kanálovém pinu paralelně pro přesné měření času programu stránky.

Vyvinutá testovací metodika zahrnovala použití API Rapid Development Interface (RDI), což je kódová struktura, která obaluje standardní aplikační programovací rozhraní (API) společnosti Advantest. API je založeno na objektově orientovaném programování, které zapouzdřuje příkazy firmwaru a umožňuje bezproblémové provádění více příkazů. To vytváří konkurenční výhodu dramatickým zefektivněním vývoje softwaru a díky víceportové schopnosti V93000 umožňuje vyšší rozlišení časování, kterého lze dosáhnout na konkrétním pinu nebo skupině pinů. Použití funkce komparátoru umožňuje bliknout pro změnu úrovně signálu po pevně stanovenou dobu.

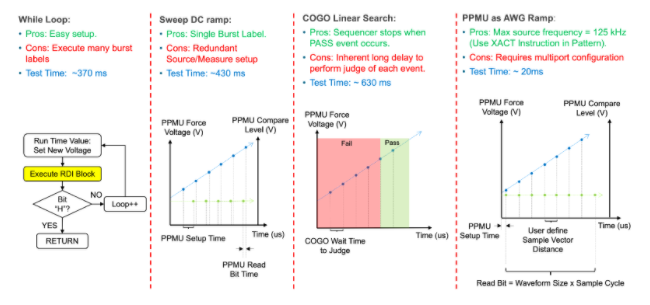

Power Management

Detekční obvod Brownout v PEPS je výzvou k testování, aby bylo dosaženo optimální doby testu. V typické testovací metodě se provádí rozmítání napětí od vysokého k nízkému, aby se detekoval práh stavu vybití, následovaný rozmítáním napětí od nízkého k vysokému pro hledání prahové úrovně obnovy. Byl proveden experiment s implementací čtyř různých testovacích metodologií s cílem určit nejoptimalizovanější metodu pro testování obvodu detekce Brownout, která je shrnuta na obrázku 3. Souhrnně lze říci, že implementace parametrické měřicí jednotky Per Pin (PPMU) jako generátoru libovolného tvaru vlny (AWG) poskytl nejrychlejší testovací čas s minimální závislostí na latenci testovacího přístroje.

Obrázek 3: Zkoumání čtyř různých metodologií detekce brownoutu – PPMU jako metodika AWG spotřebuje zlomek testovacího času ve srovnání s ostatními třemi možnostmi

Nízkofrekvenční test

Obvod indikátoru síly signálu přijímače (RSSI) v přívěsku ukazuje blízkost a umístění přívěsku s ohledem na vozidlo. 3D LF kolíky jsou transpondéry s přenosem signálu a detekcí na frekvenci 125 kHz s úrovněmi amplitudy detekce tak nízkými, jako je špičkový rozdíl 1.0 mV. Test LF vyžaduje komplexní obvody na desce, aby bylo možné získat úrovně amplitudy AWG od 1 mV do 8 V špičkově. Vzhledem k poptávce po realitách ze strany zátěžové desky na implementaci těchto obvodů s amplitudovými rozsahy se používá zátěžová deska extra velké velikosti, která se rozprostírá na obě strany pole testeru. Hodnotu RSSI lze načíst až po dokončení převodu úrovně LF signálu z určitého registru v zařízení. Kromě toho existuje registr, který lze nepřetržitě číst pro kontrolu stavu konverze RSSI.

Proto je správnou testovací metodologií pro tento test implementace API Condition Go-No-Go (COGO) od RDI, aby se průběžně kontroloval stav konverze. Tato metoda odpovídá aplikaci zařízení. Avšak vzhledem k přirozené dlouhé latenci pro posouzení každé události pomocí COGO (popsáno na obrázku 3), bylo před načtením konverze RSSI implementováno jednorázové pevné časové zpoždění.

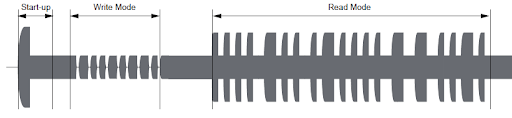

Druhý primární test LF zahrnoval transpondér, který se používá pro imobilizér. Klíčenka, která je umístěna na startovacím tlačítku vozidla, bude napájena cívkou vozidla, která je umístěna kolem startovacího tlačítka, aby byla umožněna komunikace mezi klíčenkou a vozidlem. Tento test vyžaduje jak nástroje AWG, tak digitizér (DGT), aby zdroj a zachycení modulovaného průběhu na LF kolících.

Komunikace mezi přívěskem na klíče a vozidlem se skládá ze tří fází, jak je znázorněno na obrázku 4 – spuštění (přivede klíček k napájení), režim zápisu (vozidlo přenese ověřenou zprávu na klíčenku) a režim čtení (odpovědi přívěsku s další ověřenou zprávou). Následné zpracování jak zdrojové, tak přijímané křivky využívá vlastní funkce Digital Signal Processing (DSP) spolu s vestavěnými DSP API V93000.

Obrázek 4: Komunikace transpondéru mezi klíčenkou a vozidlem na LF kolících na klíčence.

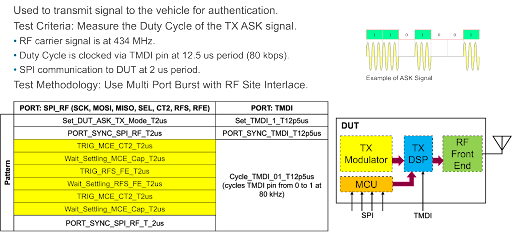

Modulace Amplitude Shift Keying (ASK) se používá k přenosu RF ověřeného signálu z přívěsku na klíče do vozidla. Je důležité otestovat pracovní cyklus modulovaného signálu, který má periodu 12.5 us, přepínanou externím pinem při nastavení v testovacím režimu. Samotné zařízení pracuje s periodou 2 us. Proto musí být implementován multiport, aby sekvencer řídil dvě skupiny portů v různých periodách. Tato testovací metodika také zahrnuje techniku prokládání vysokofrekvenčních míst, využívající výhody osmimístného paralelního testu V93000 se 2 kartami RF FE24. Obrázek 5 znázorňuje kritéria testu a použitou metodologii. Následné zpracování zahrnuje zachycení komplexního tvaru vlny, konverzi tvaru vlny na efektivní hodnotu za účelem vytvoření shlukových obálek, provádění klouzavého průměru pro odfiltrování šumu a hledání všech sestupných a vzestupných hran pro výpočet pracovního cyklu.

Obrázek 5: Metodika testu pracovního cyklu přenosu ASK je shrnuta zde.

Softwarové/hardwarové techniky

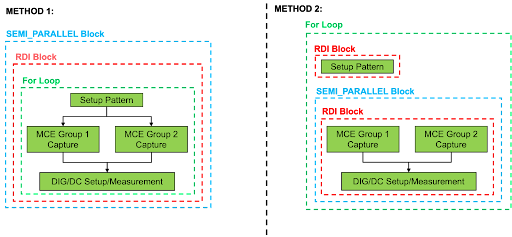

Testování LF vyžaduje sdílení nástrojů AWG a Digitizer (MCE 4 zdroje a 4 jednotky měření) na 8 místech, čímž se prodlužuje doba testování a snižuje se účinnost více pracovišť. Implementace bloku SEMI_PARALLEL v testovací metodě umožňuje provedení jediného testovacího cyklu, a tím maximalizuje efektivitu více míst. Sekvenátory připojené k AWG a DGT jsou umístěny v bloku SEMI_PARALLEL, jak je znázorněno na obrázku 6. Metoda 1 je nejběžnější implementací. Vzor nastavení však bude na stejném webu proveden více než jednou. Naopak, metoda 2 je nejméně účinná, ale může být možností, pokud lze vzor nastavení provést na každém místě pouze jednou, aby se zabránilo změně stavu zařízení.

Obrázek 6: Zde jsou zobrazeny dvě nejběžnější metody blokového testovacího toku SEMI_PARALLEL pro sdílené zdroje.

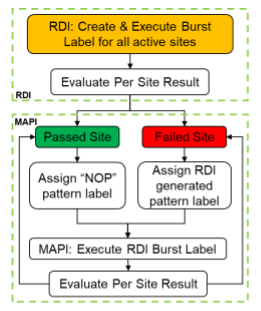

Další technika testovací metody implementovaná jako součást testovacího řešení zahrnuje použití RDI i MAPI API k vyřešení selhání zařízení na místě v konkrétním režimu nebo události, jak je znázorněno na obrázku 8. RDI se používá pro počáteční generování a provádění vzoru. . Rozhraní API MAPI se následně používají k opětovnému spuštění vzoru generovaného RDI na konkrétních neúspěšných serverech. Tato metoda umožňuje obnovení zařízení (zařízení) v rámci testovací metody, aby se ušetřila doba testování a neaplikování stimulů a opakované testování již prošlých míst.

Obrázek 7: Kombinace využití RDI a MAPI umožňuje vyřešit selhání zařízení na místě.

Na straně hardwaru umožňuje použití obvodu ovladače relé (SN74LS04DR následovaný MDC3105LT1G) současně řídit osm relé, jako je G3VM-41QR10TR05, pouze pomocí jediného pomocného kolíku. Tato technika umožňuje implementaci mnoha obvodových cest na zátěžové desce, ale vynechává potřebu karty PMUX v testeru. Následně návrh testovací zátěžové desky vyžaduje kalibraci každé signálové cesty a obvodu pro každé testovací místo. Na desce je EEPROM, která ukládá kalibrační offset a ztráty. Vzhledem k omezené kapacitě paměti v EEPROM je každá kalibrační hodnota komprimována pomocí standardu IEEE754 s pohyblivou řádovou čárkou. V závislosti na požadavku na přesnost tato metoda umožňuje větší než 50% hodnocení komprese desetinné hodnoty.

Stručně řečeno, existuje mnoho výzev ve vývoji hardwaru i softwaru, jak vytvořit testovací řešení pro optimalizovanou dobu testování a efektivitu, jak je shrnuto na obrázku 8.

Obrázek 8: Shrnutí a výzvy řešení testu klíčenky PEPS.

Vzhledem k tomu, že toto zařízení je určeno pro automobilové aplikace, musí být testováno při nízkých, pokojových a vysokých teplotách. Změny teploty ovlivňují výkon obvodů na zátěžové desce a musí být kalibrovány pro každý teplotní rozsah. Jádro MCU musí být testováno na více různých úrovních napětí, což vyžaduje synchronizaci sekvenceru vzoru pro každou změnu úrovně. Kromě toho testování LF obvodu vyžaduje rozsáhlé změny v úrovni amplitudy AWG, což vyžaduje dodatečné nastavení a dobu provádění, což může prodloužit dobu testování a snížit účinnost.